[기본회로] D 플립플롭을 사용하여 10진수 카운트 설계 이론

[기본회로] D 플립플롭을 사용하여 10진수 카운트 설계 이론

[기본회로] D 플립플롭을 사용하여 10진수 카운트 설계 이론

D 플립플롭을 사용하여 10진수 카운트 설계 이론

기본이론

플립플롭 이란

- 플립플롭은 2진 부호 0또는 1을 기억하는 최소 기억 소자이다.

플립플롭은 입력 신호를 변경하지 않는다면 일단 기억된 정보는 계속

유지된다.

- 입력 신호 외에 출력에 영향을 주는 클록(Clock) 펄스의 유무에 따라

비동기식 플립플롭과 동기식 플립플롭으로 구분된다.

D 플립플롭 이란

- 입력 신호 D가 출력 신호 Q에 그대로 전달되고

Q 는 Q값의 반대로 출력되는 특성을 가지고 있는 플립플롭이다.

- 클록 펄스가 0이면 High impedance가 되어 전체가 동작 불능이 되고

클록 펄스가 1인 상태에서 동작한다.

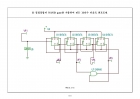

D 플립플롭(NAND 게이트형)

회로도

블록도

특성표

입력

출력

CP

DQQ0XXX10011110

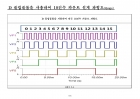

D 플립플롭의

파형도

10진수 카운트 설계 이론

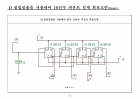

1. D 플립플롭 4개를 사용하여 4bit 16진수 카운트를 설계한다,

(회로도 2-1참고)

2. 16진수 카운트는 2진수 ‘0000’에서 ‘1111’까지 설계되어 있다.

이 설계를 10진수 카운트인 2진수 ‘0000’에서 ‘1001’까지 설계하기

위해 11진수의 마지막인 ‘1010’에서 비동기시 Nand gate를 사용한다.

3. Nand gate는 두 입력이 ‘1’과 ‘1’일때만 출력값이 ‘0’이되고, 다른

입력엔 출력이 무조건 ‘1’이 나온다. 이 특성을 이용하여 D 플립플롭을

0으로 초기화하는 CLR입력단자에 Nand gate의 출력단자를 연결한다.

(여기서 CLR이란, CLEAR의 뜻으로 D 플립플롭 안에 기억된 값을

‘0’으로 초기화 시킬 수 있는 입력단자이다.

이 외에 PR이라는 입력단자도 있는데 이 입력단자는 PRESET의 의미로

....

기본이론

플립플롭 이란

- 플립플롭은 2진 부호 0또는 1을 기억하는 최소 기억 소자이다.

플립플롭은 입력 신호를 변경하지 않는다면 일단 기억된 정보는 계속

유지된다.

- 입력 신호 외에 출력에 영향을 주는 클록(Clock) 펄스의 유무에 따라

비동기식 플립플롭과 동기식 플립플롭으로 구분된다.

D 플립플롭 이란

- 입력 신호 D가 출력 신호 Q에 그대로 전달되고

Q 는 Q값의 반대로 출력되는 특성을 가지고 있는 플립플롭이다.

- 클록 펄스가 0이면 High impedance가 되어 전체가 동작 불능이 되고

클록 펄스가 1인 상태에서 동작한다.

D 플립플롭(NAND 게이트형)

회로도

블록도

특성표

입력

출력

CP

DQQ0XXX10011110

D 플립플롭의

파형도

10진수 카운트 설계 이론

1. D 플립플롭 4개를 사용하여 4bit 16진수 카운트를 설계한다,

(회로도 2-1참고)

2. 16진수 카운트는 2진수 ‘0000’에서 ‘1111’까지 설계되어 있다.

이 설계를 10진수 카운트인 2진수 ‘0000’에서 ‘1001’까지 설계하기

위해 11진수의 마지막인 ‘1010’에서 비동기시 Nand gate를 사용한다.

3. Nand gate는 두 입력이 ‘1’과 ‘1’일때만 출력값이 ‘0’이되고, 다른

입력엔 출력이 무조건 ‘1’이 나온다. 이 특성을 이용하여 D 플립플롭을

0으로 초기화하는 CLR입력단자에 Nand gate의 출력단자를 연결한다.

(여기서 CLR이란, CLEAR의 뜻으로 D 플립플롭 안에 기억된 값을

‘0’으로 초기화 시킬 수 있는 입력단자이다.

이 외에 PR이라는 입력단자도 있는데 이 입력단자는 PRESET의 의미로

....

-

순서 논리회로 설계

순서 논리회로 설계

순서 논리회로 설계 목 차 설계 목표 관련 기술 및 이론 설계 내용 및 방법 회로 설계 결과 토의 설계 목표 우리 주변에서 순서 논리 회로를 이용하여 설명되거나, 설명할 수 있는 제품이나 놀이를 생각해 .. -

디지털 공학-플립플롭ppt

디지털 공학-플립플롭ppt

1 디지털공학 2 제 10 장 플립플롭 이 장에서는 디지털 상태(1, 0)로 latch가 되는데 인터 저장회로를 취급하게 된다. 이 새로운 형태의 디지털 회로는 순차회로(Sequential circiut)라고 부른다. 가장 간단한 저.. -

[한국반도체산업협회-면접] 반도체 RTL 설계 전문가 양성과정 면접기출, 1분 자기소개, 압박질문답변, 2025면접족보

[한국반도체산업협회-면접] 반도체 RTL 설계 전문가 양성과정 면접기출, 1분 자기소개, 압박질문답변, 2025면접족보

RTL 설계 직무에서 가장 중요하다고 생각하는 역량은 무엇입니까 RTL 설계 직무에서 가장 중요한 역량은 첫째 구조적 사고, 둘째 정확성, 셋째 검증 중심의 태도라고 생각합니다. RTL 설계에서는 이 둘을 명확히 .. -

[Verilog프로그래밍]D래치, 플리플롭, shift register

[Verilog프로그래밍]D래치, 플리플롭, shift register

1. 목적 Verilog의 연속할당문을 사용한 래치 설계 방법과 always 문을 사용한 동작적 모델링 방 법의 래치, 플립플롭 설계 방법을 익히고 이를 간단한 회로의 설계에 적용한다. 2. 기초지식 - feedback이 있는 da.. -

반가산기및전가산기

반가산기및전가산기

실험 5. 반가산기 및 전가산기 1. 목적 (1) 반가산기와 전가산기의 설계를 통해 조합논리회로의 설계방법을 공부한다. (2) 설계된 회로의 기능측정 2. 이론 다음과 같은 2진수 2개를 더하는 경우에 대해 고찰해 .. -

디지털공학 - 논리 함수의 간략화 및 7-Segment

디지털공학 - 논리 함수의 간략화 및 7-Segment

디지털 공학 실험보고서 [논리 함수의 간략화 및 7-Segment] 실험의 목적 드-모르간의 정리를 실험적으로 증명하고, 논리회로의 간략화를 보인다. 7-Segment의 원리와 숫자 표시기의 사용방법을 익힌다. 사용.. -

논리회로 설계 및 실험 - 가산기와 감산기

논리회로 설계 및 실험 - 가산기와 감산기

논리회로 설계 및 실험 - 가산기와 감산기 [각 사진마다 LED는 ☆로, 스위치는 ↑로 표시해 놓았습니다.] ⓵ 7486 IC, 7408 IC 으로 구현한 가산기 회로 반가산기는 2개의 2진 입력과 2개의 2진 출력이 필요하다. .. -

[디지털공학] 예비보고서 - 플립플롭

[디지털공학] 예비보고서 - 플립플롭

1.실험 제목 플립플롭 2.실험 목적 순서논리회로의 기반이 되는 플립플롭을 RS, D, T, JK , 주종플립플롭 등을 대상으로 하여 동작 원리를 살펴보고 전반적인 이해를 도모하도록 한다. 3.관련 이론 (1)RS 플.. -

N진 카운터 및 10진 카운터

N진 카운터 및 10진 카운터

Ⅱ.목적 1.케스케이드된 T-FF을 사용하여 2의 지수가 아닌 카운트값에 의해 입력 주파수를 분주하는 카운터에 대해 공부한다. 2.이들 카운터의 카운트 상태에 대해 공부한다. 3.가중된(weighted BCD 10진 카운터.. -

RS 및 D Flip Flop JK 및 T Flip Flop 발표 자료

RS 및 D Flip Flop JK 및 T Flip Flop 발표 자료

RS 및 D Flip Flop JK 및 T Flip Flop Flip Flop 이란 플립플롭은 두 가지 상태 사이를 번갈아 하는 전자회로이다. 플립플롭에 전류가 부가되면,현재의 반대 상태로 변하며 (0 에서 1 로,또는 1 에서 0 으로), 그 ..