RS 및 D Flip Flop JK 및 T Flip Flop 발표 자료

RS 및 D Flip Flop JK 및 T Flip Flop 발표 자료

RS 및 D Flip Flop JK 및 T Flip Flop 발표 자료

RS 및 D Flip Flop JK 및 T Flip Flop

Flip Flop 이란

플립플롭은 두 가지 상태 사이를 번갈아 하는 전자회로이다. 플립플롭에 전류가 부가되면,현재의 반대 상태로 변하며 (0 에서 1 로,또는 1 에서 0 으로), 그 상태를 계속 유지하므로 한 비트의 정보를 저장할 수 있는 능력을 가지고 있다. 여러 개의 트랜지스터로 만들어지며 SRAM이나 하드웨어 레지스터 등을 구성하는데 사용 플립플롭에는 RS 플립플롭, D 플립플롭, JK 플립플롭, T 플립플롭 등 여러 가지종류가 있다.

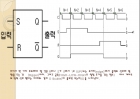

RS Flip Flop

....

Flip Flop 이란

플립플롭은 두 가지 상태 사이를 번갈아 하는 전자회로이다. 플립플롭에 전류가 부가되면,현재의 반대 상태로 변하며 (0 에서 1 로,또는 1 에서 0 으로), 그 상태를 계속 유지하므로 한 비트의 정보를 저장할 수 있는 능력을 가지고 있다. 여러 개의 트랜지스터로 만들어지며 SRAM이나 하드웨어 레지스터 등을 구성하는데 사용 플립플롭에는 RS 플립플롭, D 플립플롭, JK 플립플롭, T 플립플롭 등 여러 가지종류가 있다.

RS Flip Flop

....

-

[디지털공학] 플립플롭을 이용한 신호등 제어기 작성

[디지털공학] 플립플롭을 이용한 신호등 제어기 작성

목표 : 플립플롭을 이용한 신호등 제어기 작성. ◆ Flip-Flop 4bit동기 업 카운터를 만들기 위하여 JK F/F를 사용. ●FLIP FLOP-클럭 펄스가 나타나기 바로 이전의 입력이 출력에 반영되어 다음 클럭 펄스가 나타.. -

디지털 공학-플립플롭ppt

디지털 공학-플립플롭ppt

1 디지털공학 2 제 10 장 플립플롭 이 장에서는 디지털 상태(1, 0)로 latch가 되는데 인터 저장회로를 취급하게 된다. 이 새로운 형태의 디지털 회로는 순차회로(Sequential circiut)라고 부른다. 가장 간단한 저.. -

논리회로 - 플립플롭

논리회로 - 플립플롭

플 립 플 롭 플립플롭과 래치는 두개의 안정된 상태 중 하나를 가지는 1비트 기억소자 플립-플롭 클럭신호가 Rising 할 때만 출력값이 변함. Edge-triggered 방식으로 동작 래치 Enable 제어신호가 ‘1’인 동안에.. -

[디지털 회로 설계] 4-Bit D Flip Flop 설계

[디지털 회로 설계] 4-Bit D Flip Flop 설계

디지털 회로설계 1. 제목 : 4-Bit D Flip Flop 설계 2. 개요 : 1) 목적 : 1 bit flip flop을 통해 4 bit flip flop을 VHDL과 logic gate로 설계한다. 이 과정에서 VHDL의 process의 사용법을 익히고, logic gat.. -

[디지털 시스템 설계 및 실험] Latch, Flip-Flop, Shift Register

[디지털 시스템 설계 및 실험] Latch, Flip-Flop, Shift Register

디지털 시스템 설계 및 실험 결과보고서 실험제목 Latch, Flip-Flop, Shift Register 실험목표 1. SR NOR latch 2. Gated D latch(based on an SR NOR latch) 3. (Masterslave pulse-triggered) D flip-flop (wit.. -

[디지털 회로설계] 4-Bit D Flip Flop 설계

[디지털 회로설계] 4-Bit D Flip Flop 설계

디지털 회로설계 1. 제목 : 4-Bit D Flip Flop 설계 2. 개요 : 1) 목적 : 1 bit flip flop을 통해 4 bit flip flop을 VHDL과 logic gate로 설계한다. 이 과정에서 VHDL의 process의 사용법을 익히고, logic gate.. -

플립플롭(Flip-Flop)

플립플롭(Flip-Flop)

◎ 플립플롭 대다수 놀리 회로들은 그들의 출력 값들이 현재 상태의 입력뿐만 아니라, 이전 상태의 값에 의해서 그 결과가 결정되는 성격을 갖는다. 이런 성격의 논리 회로들을 순차 회로라고 한다. 순차 회로.. -

[디지털 회로실험] 비동기 카운터

[디지털 회로실험] 비동기 카운터

비동기 카운터 본 실험에서는 리플카운터의 기본형에 대하여 실험하고 모듈의 정의를 소개한다. 1. 서 론 비동기 카운터는 플립플롭을 직렬로 연결하여 구성하며 한 플립플롭의 출력은 그다음 플립플롭의 입력에.. -

설계과제 - 야구 스코어보드 설계

설계과제 - 야구 스코어보드 설계

Baseball Score Board System (Last) 개 발 조 건 1 사 용 부 품 2 설 계 4 목 차 사 용 소 자 의 특 성 3 회 로 도 5 제 작 과 정 6 최종시연 보고 및 평가 7 스트라이크에 대한 두 개의 등(LED)과 볼에 대한 세 .. -

[전자공학] N체분계수기와 10진계수기 Shift Register와 Ring Counter

[전자공학] N체분계수기와 10진계수기 Shift Register와 Ring Counter

N체분계수기와 10진 계수기 Shift Register와 Ring Counter N체분 계수기와 10진계수기 1. 목적 1) T Flip-Flop을 P단 직렬접속한 계수기로서 보다 적은 다른 인수로 입력 주파수를 체분하는 계수에 대한 학습 ..