순서회로

순서회로

순서회로

순서논리회로 설계

폰 응답 머신을 제어하는 순서회로를 설계한다.

세 개의 입력 R, A, S와 한 개의 출력 Z를 가진다.

각 폰 울림의 끝에서 한 클럭 사이클 동안 R=1이다.

입력 A는 폰의 응답 여부를 나타낸다. 폰이 응답할 때, A=1이다.

S는 머쉰이 2번 울리거나(S=0) 또는 4번 울린(S=1) 후 폰에 응답해야 하는지를 선택한다.

레코더가 폰에 응답하도록 야기시키기 위해, 회로는 2번 울리거나 또는 4번 울린 뒤에, 출력 Z=1을 설정하고 레코더가 폰에 대답할 때까지(A가 1로 갈 때) Z=1을 유지한다.

만약 어떤 시점에서 사람이 폰에 응답한다면, A는 1이 될 것이고, 회로는 리셋된다.

폰이 울림을 세는 동안 S는 변하지 않는다.

1. 설계배경 및 목표

1) D - FlipFlop

하나의 입력 단자가 있고 클록 펄스가 인가되었을 때 입력 신호가

1이면 1로, 0이면 0으로 자리잡는 플립플롭. 일반적으로 입력 신호

를 클록 펄스의 시간 간격만큼 지연시켜 출력으로 내는 데 사용된다.

표는 동기식 D 플립플롭의 입력값과 출력값의 관계를 나타낸 것이

다. Qn+1은 n+1번째의 클록 펄스에 의한 출력을 표시한다.

2. 관련 기술 및 이론

1) 상태그래프

3. 설계 내용

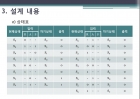

2) 상태표

3. 설계 내용

3) 천이표

3. 설계 내용

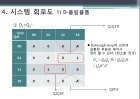

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q1Q3’R

Q1R’A’

Q2Q3R

① D1=Q1+

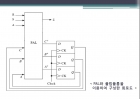

4. 시스템 회로도 1) D-플립플롭

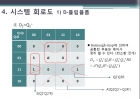

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q2’Q3R

A’(Q2Q3’+Q2R’)

S(Q1’Q2’R)

② D2=Q2+

4. 시스템 회로도 1) D-플립플롭

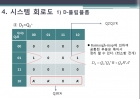

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q2’Q3’R

Q3R’A’

③ D3=Q3+

4. 시스템 회로도 1) D-플립플롭

....

폰 응답 머신을 제어하는 순서회로를 설계한다.

세 개의 입력 R, A, S와 한 개의 출력 Z를 가진다.

각 폰 울림의 끝에서 한 클럭 사이클 동안 R=1이다.

입력 A는 폰의 응답 여부를 나타낸다. 폰이 응답할 때, A=1이다.

S는 머쉰이 2번 울리거나(S=0) 또는 4번 울린(S=1) 후 폰에 응답해야 하는지를 선택한다.

레코더가 폰에 응답하도록 야기시키기 위해, 회로는 2번 울리거나 또는 4번 울린 뒤에, 출력 Z=1을 설정하고 레코더가 폰에 대답할 때까지(A가 1로 갈 때) Z=1을 유지한다.

만약 어떤 시점에서 사람이 폰에 응답한다면, A는 1이 될 것이고, 회로는 리셋된다.

폰이 울림을 세는 동안 S는 변하지 않는다.

1. 설계배경 및 목표

1) D - FlipFlop

하나의 입력 단자가 있고 클록 펄스가 인가되었을 때 입력 신호가

1이면 1로, 0이면 0으로 자리잡는 플립플롭. 일반적으로 입력 신호

를 클록 펄스의 시간 간격만큼 지연시켜 출력으로 내는 데 사용된다.

표는 동기식 D 플립플롭의 입력값과 출력값의 관계를 나타낸 것이

다. Qn+1은 n+1번째의 클록 펄스에 의한 출력을 표시한다.

2. 관련 기술 및 이론

1) 상태그래프

3. 설계 내용

2) 상태표

3. 설계 내용

3) 천이표

3. 설계 내용

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q1Q3’R

Q1R’A’

Q2Q3R

① D1=Q1+

4. 시스템 회로도 1) D-플립플롭

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q2’Q3R

A’(Q2Q3’+Q2R’)

S(Q1’Q2’R)

② D2=Q2+

4. 시스템 회로도 1) D-플립플롭

Karnaugh-map에 의하여

공통된 부분은 묶어서

정리 할 수 있다. (최소항 전개)

Q2’Q3’R

Q3R’A’

③ D3=Q3+

4. 시스템 회로도 1) D-플립플롭

....

-

GATE 논리회로

GATE 논리회로

GATE 논리회로 1. 논리회로(Logic Circuit) ― 2진 정보를 기반으로 AND, OR, NOT 등과 같은 논리 연산에 따라 동작을 수행하는 논리소자들을 사용하여 구성된 전자회로. 2. 논리회로의 분류 1) 조합논리회로(Co.. -

전기전자 회로 이론 실험 - 테브낭 정리

전기전자 회로 이론 실험 - 테브낭 정리

테브낭 정리 실험 목적 1.선형저항성 회로망을 테브낭 등가회로로 변환한다. 2.여러 가지 부하저항의 효과를 비교함으로써 [목적 1]의 회로망과 테브낭 회로가 등가인 것을 증명한다. 실험 순서 1.[표 12-1.. -

기초회로실험(예비+결과) - 노턴의 정리

기초회로실험(예비+결과) - 노턴의 정리

노턴의 정리 1. 실험목적 ⑴ 한 개 또는 그 이상의 전압원을 가지는 직류 회로에서 노턴의 정전류원 IN과 노턴의 전류원 저항 RN의 값을 확인한다. ⑵. 두 개의 전압원을 가지는 복잡한 직류 회로망의 해석에 있어 .. -

물리학 실험 - RLC 공진회로와 대역필터

물리학 실험 - RLC 공진회로와 대역필터

1. 실험 제목 : RLC 공진회로와 대역필터 2. 실험 목적 - 본 실험을 통해 ■ RLC 공진회로에 대한 기본 개념과 이론을 파악한다. ■ Q factor, Cut-off 주파수 등 공진회로의 특성을 알아본다. ■ RLC 회로의 공진 .. -

물리학 실험 - 직렬, 병렬 회로의 저항

물리학 실험 - 직렬, 병렬 회로의 저항

1. 실험 제목 : 직병렬 회로의 저항 2. 실험 목적 - 본 실험을 통해 ∎직병렬 회로에서 전류와 전압 그리고 저항의 관계를 이해한다. ∎옴의 법칙과 키르히호프 법칙을 이용하여 측정값을 이론적으로 확인해 본.. -

전기공학 기초 실험 - 회로와 기본법칙

전기공학 기초 실험 - 회로와 기본법칙

[ 회로와 기본법칙 ] *목적: 1. 직렬회로에서 전압 및 전류의 관계를 이해한다. 2. Ohm 및 Kirchhoff법칙을 이해하고 회로의 적용하는 방법을 이해한다. 3. 회로의 직류 전압 및 전류 측정법을 이해한다. 4. .. -

순서 논리회로 설계

순서 논리회로 설계

순서 논리회로 설계 목 차 설계 목표 관련 기술 및 이론 설계 내용 및 방법 회로 설계 결과 토의 설계 목표 우리 주변에서 순서 논리 회로를 이용하여 설명되거나, 설명할 수 있는 제품이나 놀이를 생각해 .. -

[전자공학] 테브낭 정리

[전자공학] 테브낭 정리

테브낭 정리 목차 실험 목적 이론요약 실험순서 및 보고서 결과 분석 및 결론 고찰 참고문헌 실험 목적 1. 선형저항성 회로망을 테브낭 등가회로로 변환한다. 2. 여러 가지 부하저항의 효과를 비교함으로.. -

전기전자 실험 - 선형 연산 증폭기 회로

전기전자 실험 - 선형 연산 증폭기 회로

선형 연산 증폭기 회로 실험 순서 1. 반전 증폭기 a. 그림 29-5의 증폭기 회로에 대한 전압이득을 계산하라. Vo/Vi(계산값)=-5 b. 그림 29-5의 회로를 구성하라. 입력 Vi에 실효전압 1V를 인가하라. DMM을 사.. -

디지털공학 실험 - 수 체계 실험

디지털공학 실험 - 수 체계 실험

제목 수 체계 실험목표 □2진수 또는 BCD(binary code decimal) 수를 10진수로 변환. □BCD 수를 디코딩하고 7-세그먼트로 표시해 주는 디지털 시스템 구성. □모의실험용으로 결함을 만들어 놓은 회로의 고장 진단...